## Part-B (5 $\times$ 4 = 20 marks)

## Answer ANY FIVE Questions

- 21. Design a JK flip flop that behaves like a T flip flop.

- 22. Explain Programmable Read-Only Memory (PROM) in detail.

- 23. State Reed-Muller expansion theorem and mention its significance.

- 24. What is CPLD? List out its advantages and disadvantages.

- 25. Design a 4 bit Gray to Binary code convertor.

- 26. Simplify the following Boolean expression using De-Morgan's Theorem

$$(\overline{AB} + \overline{AB})(A + B)$$

27. Obtain reduced state diagram for the following state table (refer Table.1)

| Present<br>State | Nex   | t State | Output |       |  |

|------------------|-------|---------|--------|-------|--|

|                  | X = 0 | X = 1   | X = 0  | X = 1 |  |

| Α                | В     | С       | 1      | 0     |  |

| В                | F     | D       | 0      | 0     |  |

| C                | D     | Е       | 1      | 1     |  |

| D                | F     | Е       | 0      | 1     |  |

| Е                | Α     | D       | 0      | 0     |  |

| F                | В     | C       | 1      | 0     |  |

Table.1

Part-C

$$(5X 12 = 60 \text{ marks})$$

Answer ALL Questions

Implement the following expression using Shannon's Expansion Technique

$F(w,x,y,z) = w\overline{x} + \overline{x}\overline{y} + w\overline{z} + \overline{x}z$

- (b) Explain the types of hazards in combinational logic circuits. Also elaborate the ways in which hazards are detected and eliminated in a circuit.

- 29. (a) Design a Mod 8 sequential counter using D flip-flop (OR)

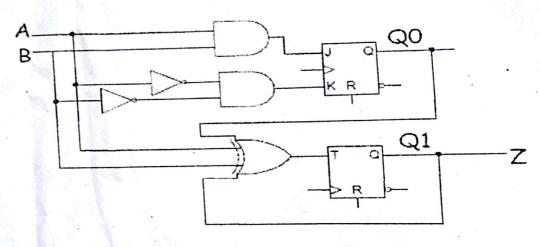

- (b) Analyze the behavior of circuit (fig.1) using state table and state diagram.

fig.1

36. (a) A Boolean function is defined by the truth table as shown Table.2. Implement the corresponding circuit with Programmab Logic Array (PLA) having three inputs, three product terms and two outputs

| A                     | В                          | C                     | $F_{\gamma}$  | $F_{\gamma}$     |  |

|-----------------------|----------------------------|-----------------------|---------------|------------------|--|

| 0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0 | 0 0 0 0 1 1 0 | 0<br>0<br>0<br>1 |  |

|                       |                            | 1_                    |               | 1                |  |

Table.2

- (b) Draw the architecture of Xilinx 4000 series FPGA and explain its Configurable Logic Block (CLB) in detail.

- 31. (a) With suitable example, explain the design and operation of a Moore sequential machine

## (OR)

- (i) Explain the concept of incompletely specified machines with an example. (10)

- (ii) Draw the logic diagram and truth table of SR flip flop (02)

(a) Implement the following multiple output logic functions

$$w(A, B, C, D) = \sum (2, 12, 13)$$

$$x(A, B, C, D) = \sum (7, 8, 9, 10, 11, 12, 13, 14, 15)$$

$$y(A, B, C, D) = \sum (0, 2, 3, 4, 5, 6, 7, 8, 10, 11, 15)$$

$$z(A, B, C, D) = \sum (1, 2, 8, 12, 13)$$

## (OR)

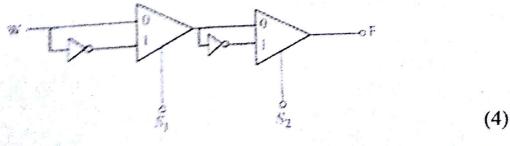

(b) (i) Find the Boolean function realized by the following circuit and show its truth table

(4)

(ii) State and prove consensus Theorem. (iii) Prove A'B + A'B'C'D'+ ABCD'= B (A' + CD') + A'C'D'.